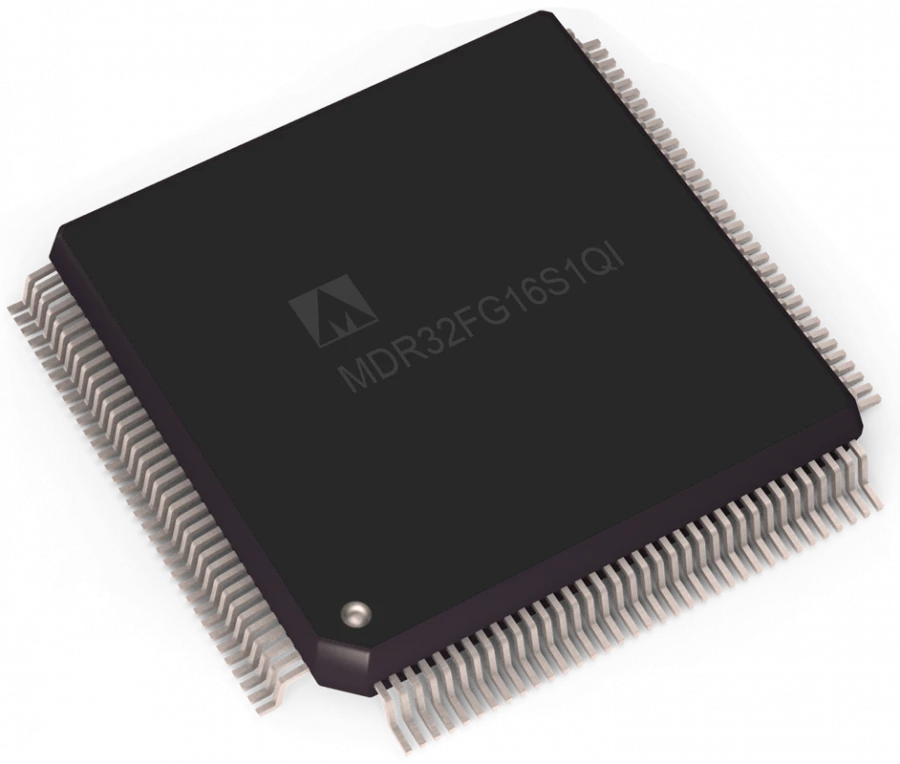

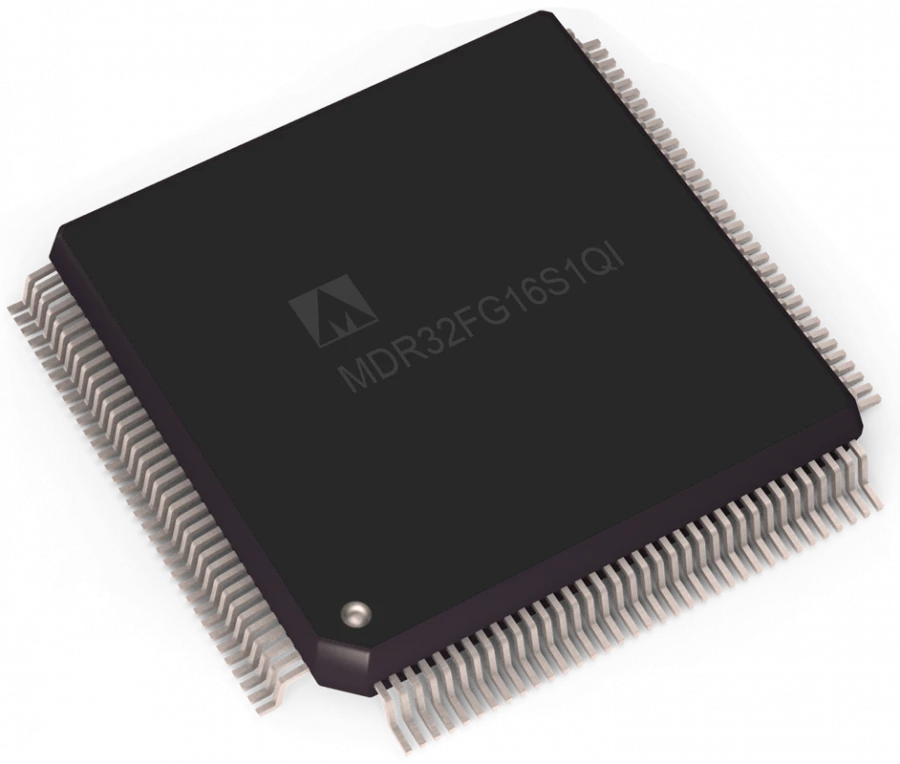

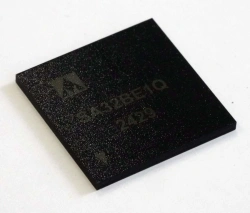

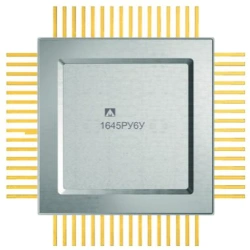

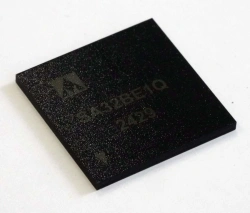

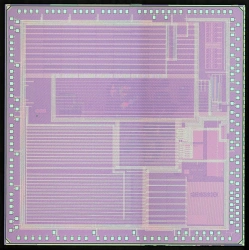

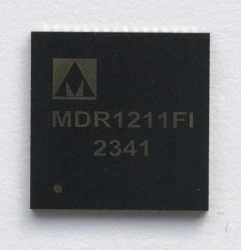

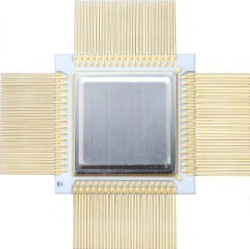

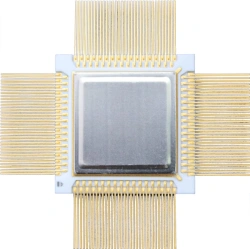

Fixed-point dual-core digital signal processor chip.

Special and professional mobile radio communications

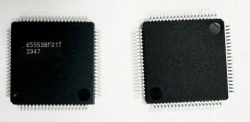

RISC subsystem core and memory features:

- 32-bit RISC core, clock speed up to 100 MHz, 1.25 DMIPS/MHz performance

(Dhrystone 2.1) with zero memory latency;

- MPU hardware memory protection unit;

- Multiplication in one cycle, hardware implementation of division;

- Built-in non-volatile FLASH type programme memory of 128 Kbytes;

- 32 Kbyte on-board RAM;

- External system bus controller with support for ROM, ROM memory chips,

NAND Flash

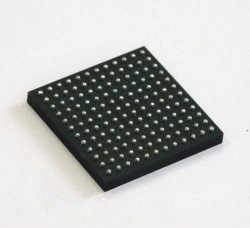

Features of DSP subsystem core and memory:

- 16-bit DSP core analogue TMS320C54, clock frequency up to 100 MHz;

- built-in RAM programme memory of 128 Kbytes in size;

- 128 Kbytes inbuilt RAM data memory;

- maximum performance at simultaneous work of RISC and DSP cores with memory

DSP subsystem

Tell us what you need and get quotes from verified suppliers